Power Supply Noise Simulation

Simulation verifies power subsystem noise which is pivotal in systems operation

Since we can determine and cope with impacts of IR drop (voltage drop) that occurs in resistance components of the board, power source impedance characteristics, or simultaneous switching noise in the design stage, we are able to develop highly reliable products. Such power source noise increases jitters in high-speed signals, degrades the reliability of signal waveforms and further leads to generation of common mode radiation noise. Reduction in power source noise is effective in improving the electric characteristics of a system. Kyocera supports reliable product design through our long experience in board design development for various fields.

Main Services

DC analysis

- Advance verification and optimization of voltage drop that occurs around VIA of high-pin-count BGA

- Verification and optimization of power layers associated with providing multiple power sources for circuits

- Optimization that includes calculation of DC resistance from the source of the power supply to the power source of IC to ensure a regulatory range of voltage fluctuation

- Optimization of the number of contact terminals for boards, packages, and chips

AC analysis

- Analysis of frequency characteristics of power source impedance and loop inductance

- Optimization of arrangement and capacity of bypass capacitors

- Switching noise analysis and optimization with bonding of signal wiring and power source wiring taken into consideration

- Power impedance and noise analysis of large current circuits in low-frequency ranges such as for motor control

Applications

- Medical equipment, network equipment, ASIC reference boards

- Automotive equipment, industrial equipment, motor control circuits for consumers

IR drop analysis

We visualize the current distribution and voltage distribution of power supply patterns. Because we can identify the presence of voltage drop and current crowding around high-pin-count BGAs, power planes and via count can be optimized at the design stage, enhancing stable operation.

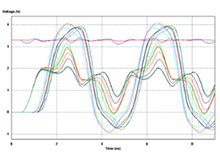

Power supply impedance analysis

We analyze the power supply impedance on frequency bands over 1GHz, and power/GND shapes and bypass capacitors are optimized if there is a resonance point. Modeling with wire bonding inside the package etc. is also available.

Analysis of low-frequency power circuit

We perform analysis of MOSFET switching noise generated by the motor control circuits like inverters, and impedance analysis on low frequencies (DC~few Hz) This is one of the new analysis issues in recent years.