Challenge: Improving Reliability and Reducing Thermal Stress During Chip-Level and Board-Level Assembly Processes

When two different materials are joined together, variation in their coefficients of thermal expansion (CTE) during the heating/cooling cycle creates stress at the joint. In microelectronics, CTE mismatch can lead to reliability challenges such as joint fracture or the detachment of assembled parts. To decrease thermal stress and improve reliability in electronic devices, it is important to match the CTE between the chip, package, and board materials. Kyocera offers a wide range of ceramic materials to accomplish this.

Ceramic Package Materials

Kyocera offers a wide range of materials with various CTE values, from those closely matching silicon to others closely matching printed circuit board materials. We can offer the optimal materials to meet your specific requirements.

CTE of Ceramic Materials

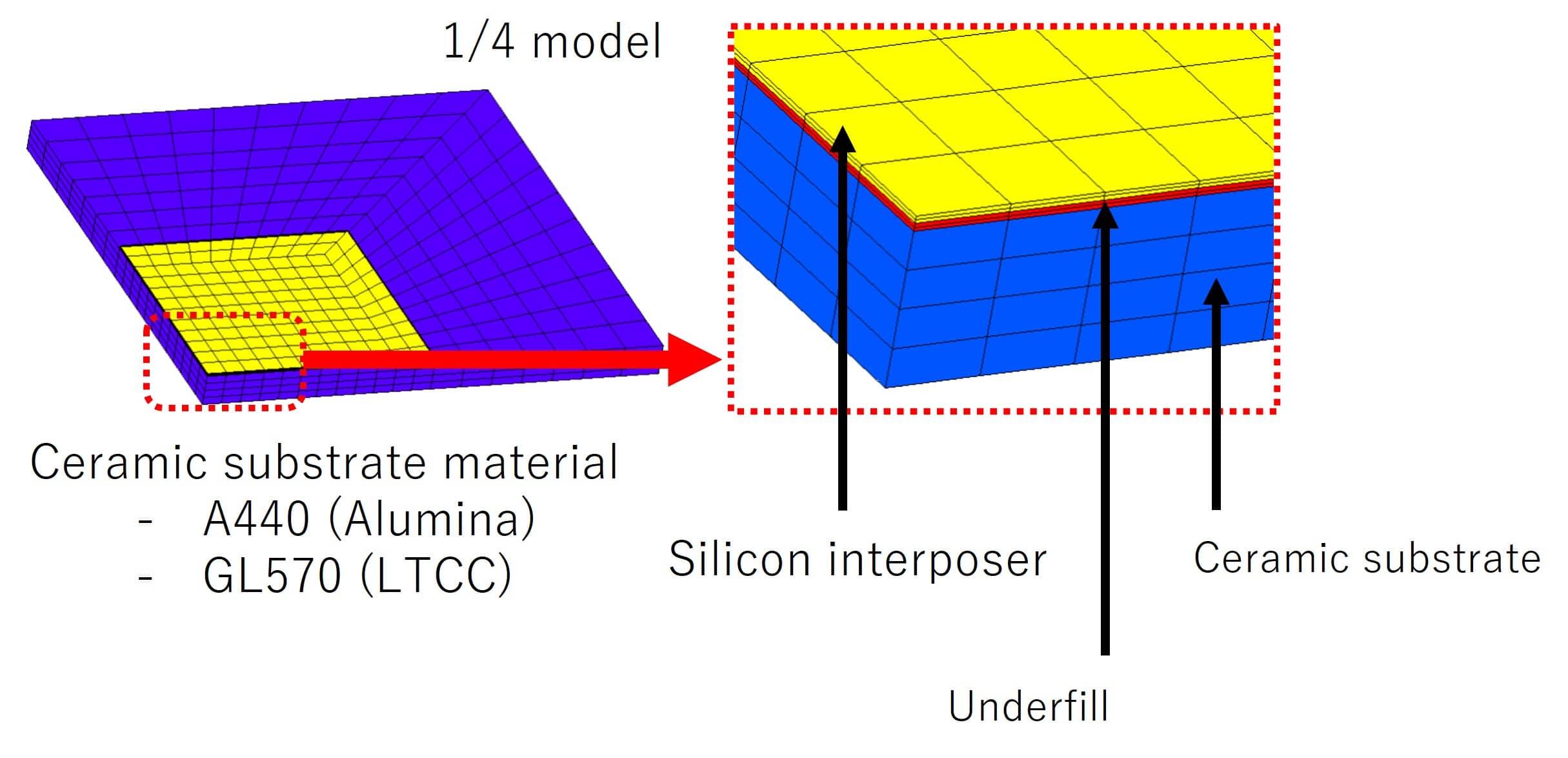

CTE Matching Simulation: GL570 and Si

We conducted a simulation to verify compatibility with Si using Kyocera's most widely adopted material, A440 (alumina), and GL570 (LTCC), which was developed to provide CTE closer to that of Si.

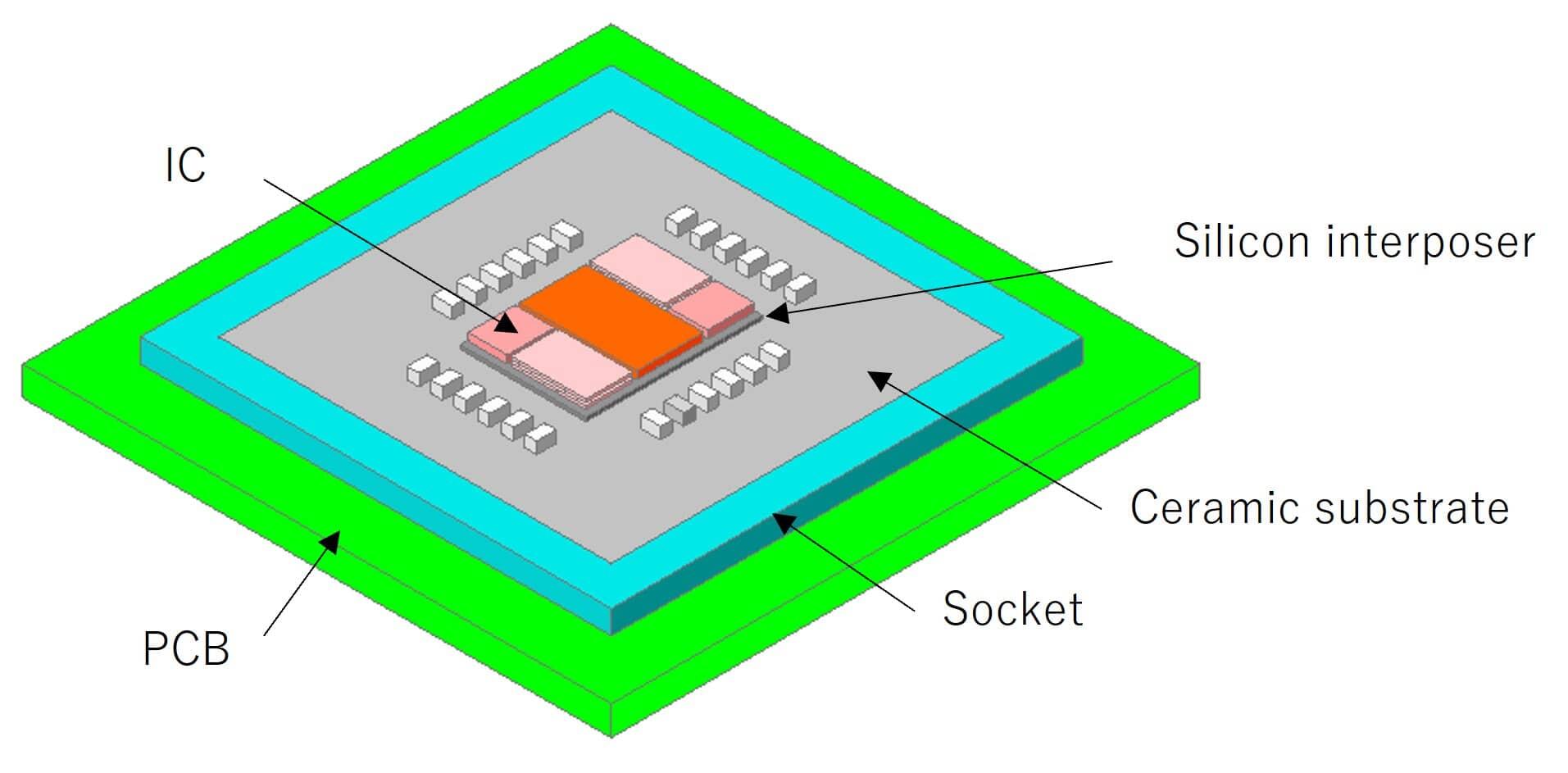

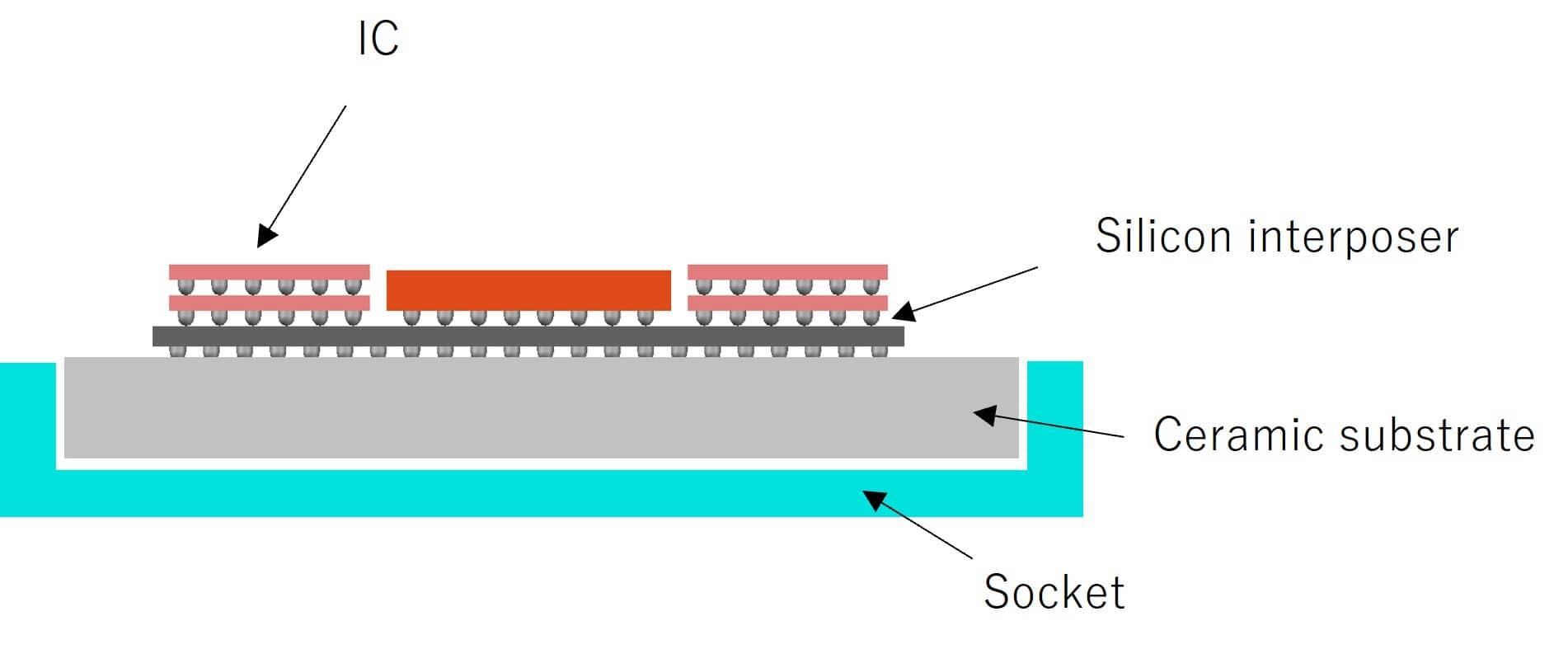

Stress Analysis of Ceramic Substrate Warpage During Underfill Reflow

Product Image

Analysis Model

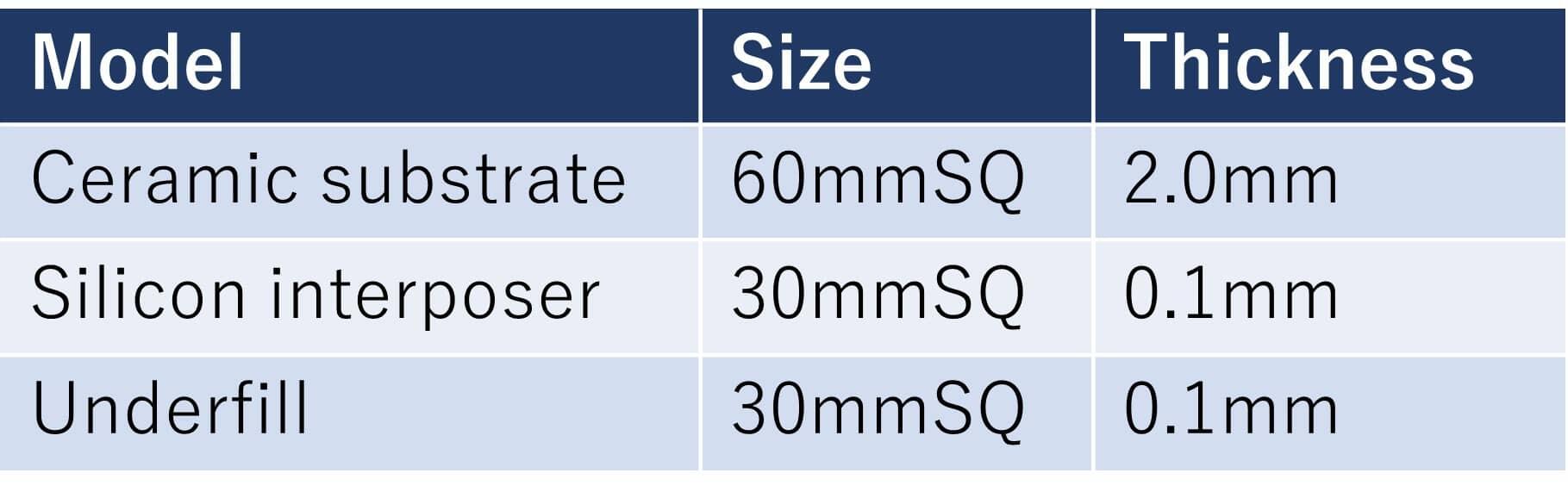

Size of Analysis Model

Analysis Condition

Cure condition of underfill: 150℃ to 20℃

Stress Analysis Results

Conclusion

Results confirm that the GL570 substrate, which has a CTE closer to that of the interposer (silicon), experienced significantly less warpage.